В мире Arm гетерогенные процессоры встречаются довольно часто, например, прикладные процессоры big.LITTLE/dynamicIQ, в которых смешиваются мощные ядра Cortex-A7x с энергоэффективными ядрами Cortex-A5x или «промышленные» процессоры, такие как семейство NXP i.MX 8M с ядрами Cortex-A53 в сочетании с ядром Cortex-M4F в реальном времени.

Может быть, мы недостаточно осведомлены, но мы действительно не видели ничего эквивалентного в мире MIPS, за исключением Ingenic T31 с ядрами RISC-V и MIPS. До сегодняшнего дня нас информировали о документах, связанных с прикладным процессором Ingenic X2000 IoT с двумя 32-разрядными ядрами MIPS Xburst 2, одним ядром реального времени MIPS Xburst 0, а также встроенной в SoC оперативной памятью объемом до 256 МБ.

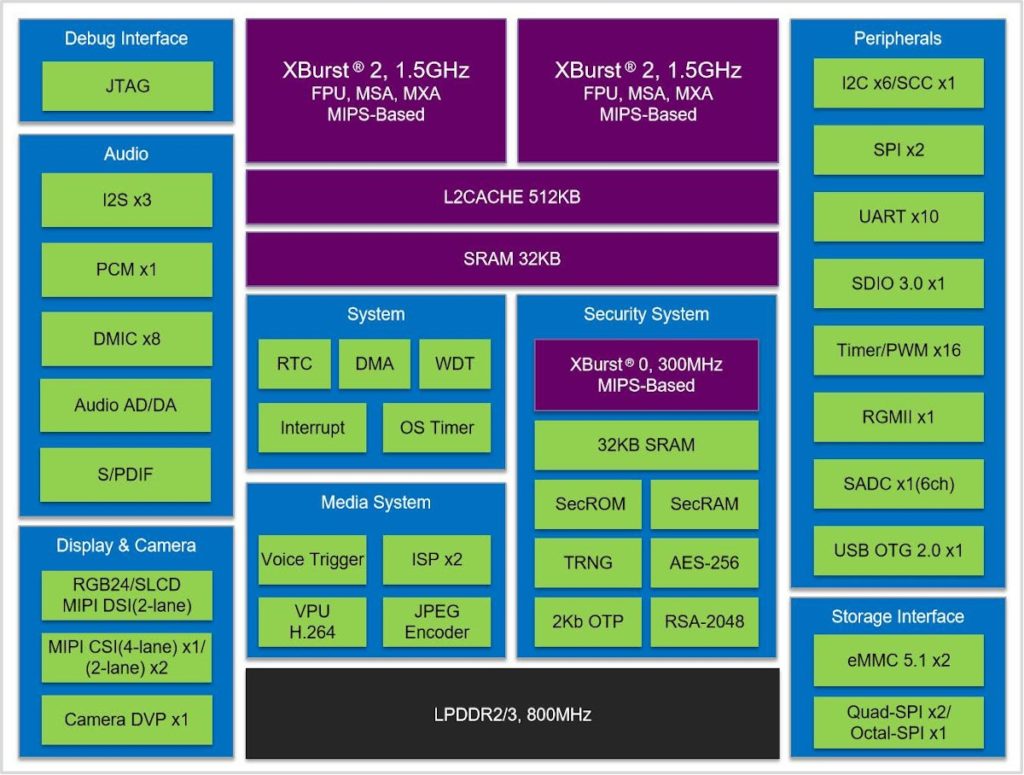

Спецификации Ingenic X2000:

- Ядро CPU – Два ядра XBurst 2 на базе MIPS ISA с тактовой частотой до 1,5 ГГц с 32 КБ кэш-памяти L1 x2, 512 КБ кэш-памяти L2, SRAM 32 КБ, FPU, 128-битная SIMD

- Ядро MCU – ядро XBurst 0 MIPS на частоте 300 МГц для обеспечения безопасности и контроля в реальном времени

- Системная память -128 / 256 МБ LPDDR2/3

- Хранилище

- SPI Flash Controller с поддержкой Quad & Octal SPI

- 2x MMC/SD/SDIO

- Дисплей

- MIPI-DSI до 1920×1080 @ 40Hz

- SLCD до 640×480 @ 60Hz, 24BPP

- RGB до 1280×720 @ 60Hz, 24BPP

- Блок обработки видео (VPU)

- Кодер / декодер H.264 с разрешением 1920x1080p30

- JPEG кодировщик / декодер до 70 мегапикселей/с

- Подсистема камеры

- Процессор обработки изображений

- 8-битный/10-битный/12-битный интерфейс YUV422 DVP до 1280 × 720 при 30 к/с

- 4-полосный или 2х 2-полосных интерфейса MIPI CSI до 1080p120

- Поддерживает синхронизацию датчика двойной камеры

- Аудио процессор

- Контроллер массива цифровых микрофонов с поддержкой 8 микрофонных каналов

- 3x I2S, PCM интерфейс, S/PDIF

- Сеть — Gigabit Media Access Controller, в соответствии с IEEE 1588-2002

- USB – 1x USB 2.0 OTG

- Безопасность — генератор случайных чисел и AES-256 / RSA-2048 / MD5 / SHA / SHA2 часть базовой подсистемы MCU

- Другие периферийные устройства

- 16x PWM

- Контроллер прерываний с поддержкой 64 источников

- Watchdog, часы реального времени

- 6-канальный 10-битный A/D преобразователь

- GPIO

- 6x I2C, 2x синхронных последовательных интерфейса (SSI)

- 10x UART

- Потребляемая мощность — 300 мВт тип.

- Размер — BGA270 — 12 х 12 х 1,2 мм, шаг 0,65 мм

- Процесс — 28 нм

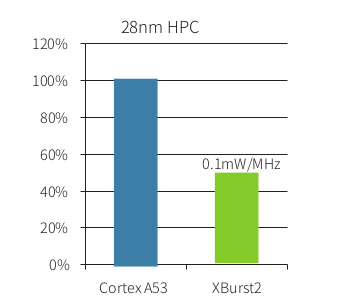

Ingenic X2000 также является самым первым процессором с ядрами XBurst 2 — ядром, которое было анонсировано много лет назад как MIPS64 (64-битное ядро MIPS), но, наконец, компания решила полностью изменить дизайн с MIPS32 ISA R5. Ingenic утверждает, что Xbust2 в два раза более энергоэффективен, чем ядро Arm Cortex-A53 с тем же 28-нм процессом.

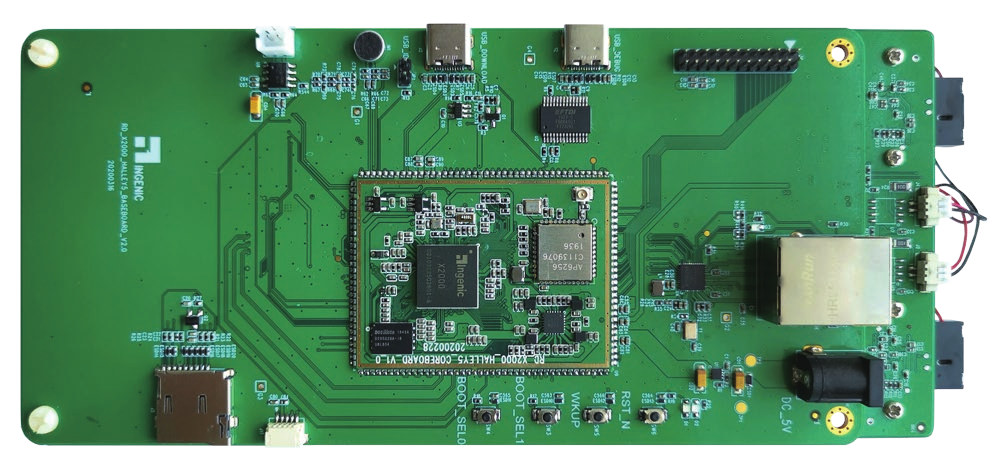

Компания может предоставить полный комплект для разработки программного и аппаратного обеспечения с платой разработки для Linux 4.4 BSP и Halley5 с SoM X2000 с беспроводным модулем, встроенным в большую несущую плату с Ethernet, USB, микрофоном, слотом для карты MicroSD, разъемом ввода-вывода, кнопки и т.д. Другая сторона платы оснащена платой с двумя камерами и AMOLED-дисплеем Full HD.

В апреле была информация о том, что MIPS пришел крах, по крайней мере, за пределами Китая идет судебный процесс и банкротство. Однако, в прошлом месяце мы все же отметили некоторые изменения, связанные с MIPS в Linux 5.7, но с очень минимальным количеством изменений. Таким образом, это должно означать, что вам придется полагаться на Ingenic BSP, и поддержка mainline очень маловероятна.

На сайте Ingenic нет страницы продукта, но у нас есть кое-что еще лучше на их FTP-сервере с кратким описанием продуктов SoC и плат и таблицей данных на английском и / или китайском языках.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.