На днях мы сообщили о универсальном 32-разрядном микроконтроллере RISC-V GigaDevice GD32V, и в одном из комментариев нас спросили это rv32imac или rv32emac, и он оказался первым. В большинстве случаев поставщики кремния сообщают, используют ли они 32-разрядные, 64-разрядные или предстоящие 128-разрядные процессоры RISC-V, но редко вдаются в подробности, поэтому мы спросили, почему это имеет значение, и получили следующий ответ:

RISC-V — это федерация расширений ISA — от базовой линии rv {32 | 64 | 128} I до произвольной комбинации нескольких расширений. Существуют комбинации, которые называются «прикладной уровень процессора» (подмножество G), но реализации могут и часто не совместимы с G, что, естественно, имеет место в MCU. Разница между rv32i и rv32e в файлах GPR 32-strong против 16-strong, соответственно. В случае GD32VF103, rv32imac означает «полноразмерный GPR-файл, целочисленное значение mul / div, атомарный, сжатый (16-битный) ISA». Чего не хватает в «уровне прикладного процессора» (G), как это в расширениях FPU — F & D.

Мы стали искать подробную информацию, и в Википедии есть хороший список ISA-баз и расширений RISC-V.

Базовые наборы RISC-V

В настоящее время существует четыре базовых набора ISA:

- RV32I — Базовый набор целочисленных инструкций, 32-разрядный. В настоящее время версия 2.1

- RV32E — Базовый набор целочисленных инструкций (встроенный), 32-разрядный, 16 регистров с меньшим набором команд. Текущая версия 1.9, но еще не заморожена

- RV64I — Базовый набор целочисленных команд, 64-разрядный. В настоящее время версия 2.0

- RV128I — Базовый набор целочисленных инструкций, 128-битный. В настоящее время версия 1.7, но еще не заморожена.

Если информация в Википедии верна, мы, скорее всего, увидим проекты RV32I и RV64I, поскольку спецификации RV32E и RV128I еще не определены.

Расширения RISC-V

Как только у нас будет базовый набор, мы можем добавить к нему расширения, чтобы определить точные характеристики ядра (замороженные расширения — по состоянию на август 2019 г. — выделены жирным шрифтом ):

- M — стандартное расширение для целочисленного умножения и деления

- A — стандартное расширение для атомарных инструкций

- F — стандартное расширение для плавающей точки одинарной точности

- D — стандартное расширение для плавающей точки двойной точности

- G — сокращение для базовых и вышеуказанных расширений

- Q — стандартное расширение для Quad-Precision с плавающей точкой

- L — стандартное расширение для десятичной плавающей запятой

- C — стандартное расширение для сжатых инструкций

- B — стандартное расширение для управления битами

- J — стандартное расширение для динамически переводимых языков, таких как C #, Go, Haskell, Java, JavaScript, OCaml, PHP, Python, R, Ruby, Scala или WebAssembly

- T — стандартное расширение для транзакционной памяти

- P — стандартное расширение для SIMD-операций

- V — стандартное расширение для векторных операций

- N — стандартное расширение для прерываний на уровне пользователя

- H — стандартное расширение для гипервизора

Первое замечание заключается в том, что многие расширения все еще находятся в стадии доработки, и, если мы правильно понимаем, поддержка таких функций, как прерывания на уровне пользователя, SIMD-операций и поддержка гипервизора, все еще разрабатывается.

Примеры «кодов» RISC-V

Мы узнали, что GD32V имеет ядро RV32IMAC. Давайте расшифруем, что это значит: GD32V — это 32-битное ядро RISC-V (RV32I) с целочисленным умножением и делением (M), атомарными инструкциями (A) и сжатыми (16-битными) инструкциями (C). Это означает, что он не имеет FPU, в этом случае это было бы ядро RV32GC (а не RV32IMACFD), если бы поддерживалась одинарная и двойная точность.

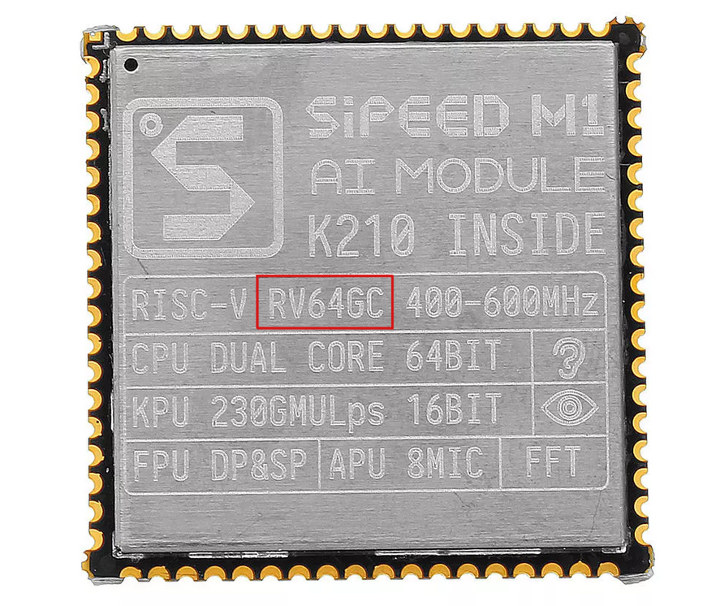

Давайте проверим еще один: двухъядерный процессор Kendryte K210 RV64IMAFDC / RV64GC: это 64-разрядный процессор RISC-V (RV64I) с целочисленным умножением и делением (M), атомарными инструкциями (A), одинарной точностью (F) и двойная точность (D) с плавающей точкой (I + M + A + F + D = G), а также сжатыми инструкциями (C).

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.