В прошлом году компания SiFive представила свои первые ядра RISC-V, конкурирующие с процессорами семейства Arm Cortex-R, благодаря 64-битному RISC-V Core IP серии S7, сравниваемому с 32-битным процессором Arm с ядрами Cortex-R7/R8 реального времени.

Теперь компания объявила о том, что ядро SiFive S2 RISC-V — это самое маленькое в мире 64-битное встроенное ядро, а также первое ядро SiFive IP, не имеющее прямого конкурентного эквивалента на рынке.

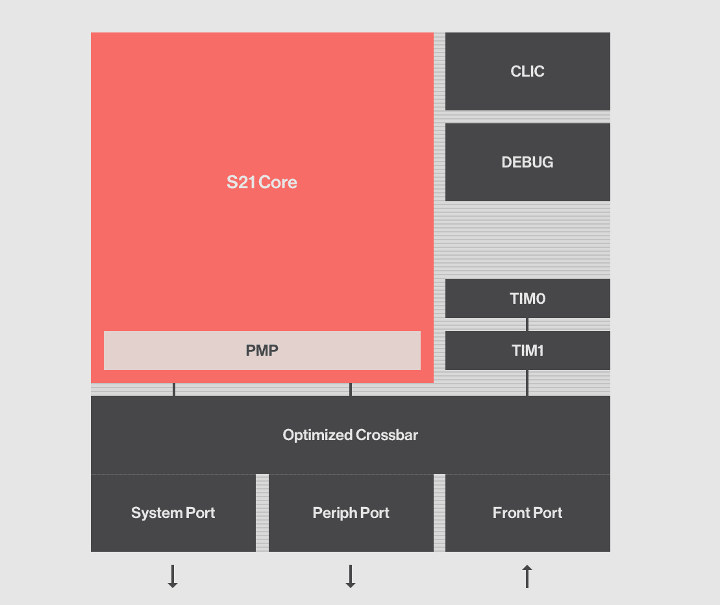

Пока в семействе есть только одно ядро с SiFive S21, со следующими ключевые характеристиками:

- RISC-V ISA — RV64IMAC

- 64-битные порты AXI

- Машинный и пользовательский режим с защитой физической памяти

- Трехступенчатый конвейер с одновременной инструкцией и доступом к данным

- 2 банка плотно интегрированной памяти (TIM)

- CLIC (основной локальный контроллер прерываний) с 127 прерываниями

- Расширенная отладка с 4 аппаратными точками останова/наблюдения

- Производительность — 1,6 DMIPS/МГц; 3.2 Coremarks/МГц

Компания сравнивает его с ядрами SiFive S5, о которых раньше не слышали, и конкурирует с ядрами Arm Cortex-R4/R5. SiFive S2 — это только половина размера аналогично сконфигурированного ядра S5, и поэтому он особенно хорошо подходит для приложений с ограниченным пространством, требующих 64-битный процессор.

Это означает, что S2 может быть найден в 64-битных встроенных контроллерах, потребительских приложениях, промышленной автоматизации или интегрирован в качестве ядра управления как часть более сложной SoC.

Более подробную информацию можно найти на странице продукта.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.