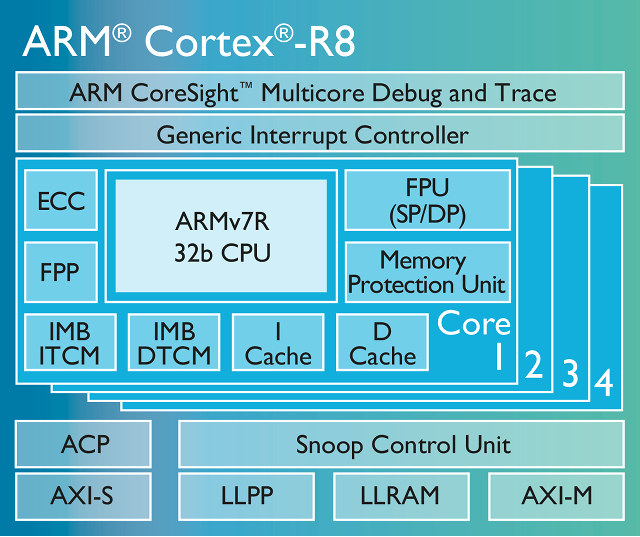

Процессор ARM Cortex-A можно встретить в популярных потребительских устройств, таких как смартфоны, но ARM также предоставляет real-time процессоры Cortex-R, которые можно будет найти в автомобилях, жестких дисках и других встраиваемых системах, требующих высокой надежности, отказоустойчивости и детерминированные ответы в реальном времени. Компания только что анонсировала Cortex-R8, ядро реального времени, оно должно удвоить производительность процессоров на ядре Cortex-R7 и предназначено, главным образом, для устройств хранения данных, таких как SSD и HDD, а также для модемов следующего поколения LTE и 5G.

Основные характеристики Cortex-R8:

- Микро-архитектура – 11- уровневая схема с инструкцией предварительной выборки, прогнозирование ветвлений, суперскалярность, порядок выполнения переходов, переименование регистров, параллельные пути выполнения загрузки-хранилища, MAC, shift-ALU, разделяющая и плавающая точка. Также есть аппаратный делитель и программная совместимость с ARM9, ARM11, Cortex-R4, Cortex-R5 и Cortex-R7 процессоры для встраиваемых систем.

- Набор инструкций – Архитектура ARMv7-R с Thumb-2 и Thumb. Поддержка DSP расширений, а также дополнительный блок операций с плавающей точкой, с одинарной или одинарной/двойной точности.

- Кэш контролеров – Гарвардская архитектура памяти с опциональной интеграцией инструкции и кэша данных контролеров. Размеры кэша конфигурируются от 4 до 64 Кб. Линии кэша обратно-записаны.

- Тесно связанная память – Опциональные интерфейсы тесно связанной памяти для сильно детерминированных приложений которые могут не реагировать на кэширование (например, код команды для обработчиков прерываний и данных, требующих интенсивной обработки). Инструкции и/или данные TCMs. Размер TCM может достигать 1 Мб.

- Интерфейс прерывания – Стандартное прерывание, IRQ, не маскируемое быстрое прерывание, FIQ, входы предусмотрены вместе с полностью интегрированными групповыми прерываниями контролера (GIC) поддерживающие комплекс на основе приоритетов обработки прерываний.

- Блок защиты памяти (MPU) – Опциональный MPU с конфигурируемыми атрибутами для 12, 16, 20 или 24 регионов, каждый с разрешением до 32 байт.

- Блок плавающей точки (FPU) – Опциональный FPU реализует ARM вектор плавающей точки архитектуры VFPv3 с 16 регистрами двойной точности, совместимые с IEEE754. Есть поддержка двух вариантов FPU.

- ECC – Опциональная коррекция одно-битных ошибок и обнаружение двух-битных ошибок для кэша и/или TCM памяти и всех интерфейсов с ECC битами.

- Мастер шина AMBA AXI – 64-битная AMBA AXI мастер шина для доступа к памяти Level-2.

- Низкая задержка порта памяти – 64-битный AMBA AXI мастер порт разработан специально для соединения с локальной памятью. Эта локальная память обеспечивает много преимуществ TCM, так же может быть медленнее и с меньшим энергопотреблением, всегда легко доступна между согласованных периферийных устройств и ядер процессора Cortex-R8.

- Низкая задержка периферийного порта (LLPP) – Общий специализированный 32-битный AMBA AXI порт для более тесной интеграции чувствительной к задержкам периферии с процессором.

- Быстрый путь порта (FPP) – Опциональный, выделенный под каждое ядро 32-битный AMBA AXI порт для более плотной интеграции чувствительной к задержкам периферии с процессором.

- Ускоритель когерентного порта (ACP) – 64-битный AMBA AXI подчиненный порт для включения конгерентности между процессором(ами) и внешней интелектуальной периферией, например DMA контролеры, Ethernet или Flexray интерфейсы.

- Подчиненная AXI шина – Опциональная 64-битная AMBA AXI шина подчиненного порта позволяющая DMA мастерам получить доступ к TCM для высокоскоростной потоковой передачи данным в и из процессора.

- Отладка – Предусмотрен порт доступа для отладки. Функциональность устройства может быть расширена с помощью CoreSight SoC-400.

- Трассировка – Интерфейс подходит для подключения к CoreSight, присутствует встроенный модуль трассировки приложений.

- Мультиядерность – Одиночная, двойная, тройная или четверная конфигурация процессора для гибкой обработки производительности в любом асимметричном мультипроцессорном режиме (AMP) или в симметричном мультипроцессорном режиме (SMP). Кроме того она может быть сконфигурирована с резервированием процессора Cortex-R8, для обнаружения отказоустойчивых/неисправных надежных систем.

- Производительность

- 1.5 ГГц + поддерживаемые частоты

- 2.50 DMIPS/МГц с Dhrystone “ground rules”, 2.90 / 3.77 DMIPS/МГц с оптимизациями

- 4.35 CoreMark/МГЦ

- Эффективность – As low as 46 DMIPS/mW

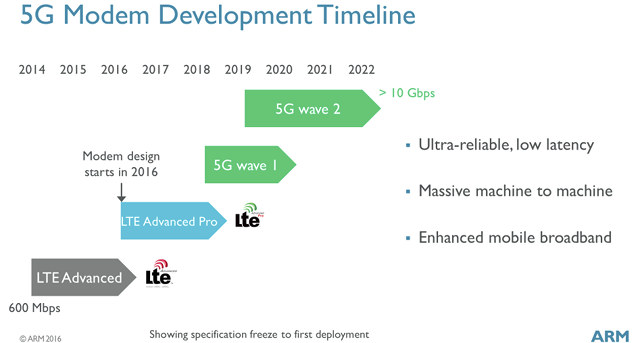

Несколько компаний уже начали работать на сокете с ядром Cortex-R8 процессоров с запоминающими устройствами на основе новых решений, которые скорее всего, станут доступны позже в этом году. Выпуск модемов на базе Cortex-R8 для стандартов LTE Advanced Pro и 5G начнется соответственно в 2017/2018 и 2019/2020. Больше информации вы сможете найти на странице продукта ARM Cortex-R8 и в ARM блоге.

Выражаем свою благодарность источнику с которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.