На днях компания Arm представила процессор с 64-битным ядром реального времени Cortex-R82, совместимый с Linux и разработанный для «корпоративных и вычислительных систем хранения следующего поколения».

Что такое вычислительное хранилище?

Чтобы четко понять, с чем мы имеем дело, давайте сначала узнаем, что такое вычислительное хранилище, на веб-сайте SNIA:

Вычислительное хранилище определяется как архитектура, предоставляющая услуги вычислительного хранилища в сочетании с хранилищем, разгружая обработку хост-системы или уменьшая перемещение данных. Служба вычислительного хранилища (CSS) — это служба данных или информационная служба, которая выполняет вычисления с данными, в которых служба и данные связаны с устройством хранения.

Итак, если мы правильно понимаем, до сих пор все, что нас интересовало о твердотельных накопителях, жестких дисках и других хранилищах — это как можно быстрее перемещать и хранить данные на хост-устройстве, способном анализировать данные. Но вычислительная память переносит это на само устройство хранения, поэтому скоро у нас могут появиться интеллектуальные жесткие диски, работающие под управлением Linux, и выполнять часть этой обработки на самом устройстве.

Arm Cortex-R82

Ключевые особенности и спецификации:

- Архитектура — Armv8-R AArch64

- Совместимость с расширениями Armv8.4-A

- Набор инструкций — набор инструкций A64

- До восьми ядер с аппаратной согласованностью в кластере

- Микроархитектура — восьмиступенчатый упорядоченный суперскалярный конвейер с прямым и косвенным предсказанием ветвлений.

- Контроллеры кеша

- Отдельный кэш данных L1 и кэш инструкций L1 для каждого ядра.

- Дополнительный общий (для всех ядер) и унифицированный (для инструкций и данных) кэш L2.

- Поддержка частичного отключения питания кеш-памяти L2.

- Tightly-Coupled Memories (TCM) — 2х дополнительных модуля TCM, принадлежащих каждому ядру: ITCM для инструкций и данных пула литералов и DTCM для данных.

- Защита кеша

- Расширение надежности, доступности и удобства обслуживания (RAS).

- Дополнительный ECC, исправление одиночной ошибки, двойной ошибки

- Защита от обнаружения (SECDED) или обнаружения двойной ошибки (DED), защита для всех инстанцированных тегов кэша и ОЗУ данных, ОЗУ TCM и ОЗУ TLB.

- Интерфейс прерывания — стандартное прерывание, IRQ, FIQ, входы предоставляются вместе с интерфейсом к внешнему универсальному контроллеру прерываний (GIC), совместимому с GICv3.2

- Блок защиты памяти (MPU)

- 2х дополнительных и программируемых MPU, управляемых EL1 и EL2, соответственно.

- Настройте атрибуты до 32 регионов на MPU. Регионы не могут пересекаться.

- Модуль управления памятью (MMU) — дополнительный модуль EL1 MMU для детального управления системой памяти с помощью сопоставления виртуальных адресов и атрибутов памяти, хранящихся в таблицах трансляции.

- Блок с плавающей запятой (FPU) и расширенный SIMD (Neon)

- Дополнительный FPU, реализующий векторную архитектуру Arm и архитектуру с плавающей запятой VFPv4 с 32 x 128-битными регистрами, совместимыми с IEEE754. Поддерживает новейший SIMD, число половинной точности, одинарной точности, двойной точности

- Master bus — Shared Main Master (MM), реализованный в виде 256-битного AXI5, обеспечивающего доступ к инструкциям, данным и периферийным устройствам. Этот интерфейс может быть дополнительно 256-битным интерфейсом CHIE.

- Slave bus – 128-битный общий порт AXIS используется для двух целей:

- В качестве порта когерентности ускорителя LRAM, обеспечивающего когерентный внешний доступ ввода-вывода к порту LRAM.

- В качестве TCM slave включение внешних агентов для доступа к TCMs в ядрах

- Порт оперативной памяти с низкой задержкой (LLRAM)-дополнительный 256-битный общий порт LLRAM AXI5, обеспечивающий доступ к инструкциям и данным с низкой задержкой. Порт предназначен для подключения к локальной памяти. Эта локальная память обеспечивает многие преимущества TCM и, кроме того, может быть медленнее и более низкой мощности, а также легко распределяется между процессорными ядрами ( до восьми).

- Общий периферийный порт (SPP)-дополнительный 64-разрядный SP AXIS 5 для обеспечения доступа к периферийным устройствам.

- Low Latency Peripheral Port (LLPP)-дополнительный для каждого ядра выделенный 32-битный порт AXI5 для тесной интеграции чувствительных к задержке периферийных устройств с конкретным ядром внутри процессора.

- Main Accelerator Coherency Port (MACP) –ACE5-Lite 128-битный общий ведомый MACP для внешнего доступа к диапазонам адресов MM. MAC обеспечивает согласованность ввода-вывода для внешних агентов с помощью кэша данных L1 для каждого ядра и общего кэша L2.

- Отладка – установлен порт Debug Access Port. Его функциональность может быть расширена с помощью Coresight Debug и Trace.

- Трассировка — Cortex-R82 включает в себя один встроенный модуль трассировки CoreSight на ядро.

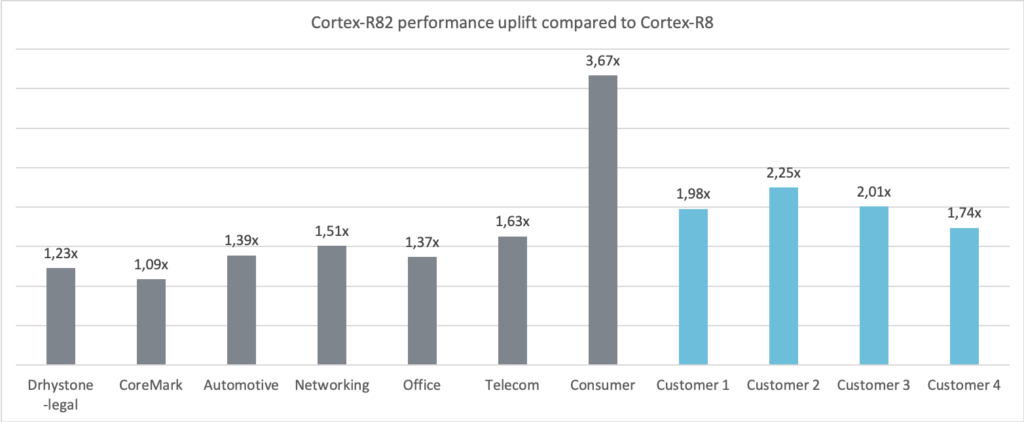

Cortex-R82 против Cortex-R8

Предыдущее ядро реального времени от Arm было 32-битным ядром Cortex-R8, а Cortex-R82 — первое 64-битное ядро реального времени от компании. Мы редко читаем об этих ядрах, поскольку они встроены в контроллеры памяти, сотовые модемы, автомобильные чипы и т. д.

В то время как Cortex-R8 ориентирован на рабочую нагрузку в реальном времени, Cortex-R82 намного мощнее и способен обрабатывать рабочие нагрузки как в реальном времени, так и на уровне приложений, и может адресовать до 1 ТБ памяти.

Ядра Cortex-A82 можно реконфигурировать на лету (с помощью программного обеспечения) для выполнения задач в реальном времени или вычислений по мере необходимости, как показано на рисунке ниже.

Уже возможно создать нечто подобное с ядрами Cortex-A под управлением Linux и ядрами Cortex-R5/R8 для обработки в реальном времени, но использование ядер Cortex-R82 упрощает общую архитектуру системы.

Сферы применения

Cortex-A82 найдет свое применение в IoT, машинном обучении и периферийных вычислениях, особенно в приложениях хранения для ускорения работы баз данных, повышения безопасности и конфиденциальности, а также перекодирования видео в реальном времени.

Arm также отметил, что вычислительная память важна для транспортировки, поскольку в настоящее время самолеты генерируют терабайты данных в день, которые необходимо выгружать для анализа. Cortex-A82 позволяет анализировать эти данные на диске в реальном времени, что ускоряет выполнение операций (30 минут).

Распознавание номерных знаков — это еще один вариант использования, который может принести пользу новому процессору, например, с системой сбора данных о номерных знаках транспортных средств в течение дня (с использованием обработки данных в режиме реального времени) и обработки данных для выставления счетов и машинного обучения (с использованием вычислительной мощности) в ночное время.

Более подробную информацию о Arm Cortex-R82 можно найти в сообществе Arm и на странице разработчика.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.